We develop ideas and build solutions to solve tomorrow’s problems. Often, many come to us with promising ideas in need of technical help to develop their concepts. The challenge with idea development is that innovation initiatives frequently fail, falling short of the idealized goal. Several reasons include a lack of understanding of the steps required for a technology to reach commercialization potential and the productization stage and the lack of a simple, actionable development system or innovation strategy. The path from an idea to a fully matured technology requires several steps and processes and almost always involves prototyping steps. (see What constitutes a prototype). The innovation and development of unproven technologies take time, often entail plenty of trial and error, and almost always require a large capacity for taking risks. It is thus essential that each step concerning the development or design of novel concepts or innovative technologies is closely managed with good decisions and done so in the absence of perfect information. Step-wise, innovation execution is essential to the success of many technological projects.

Introducing the TRL scale The Technology Readiness Level (TRL) scale is a metric for describing the maturity of a technology. The scale was introduced by NASA to assess the maturity of a technology prior to integrating it into a system. It has been gaining momentum in adoption, updated, modified and used by other agencies. Most TRL guidelines are based on a scale of 1 to 9, and overtime TRL coverage has been expanded from technical indicators to include additional dimensions of readiness metrics such as hardware and software readiness, system readiness, manufacturability, and ease of integration and even commercial adoption. Further reference links are cited at the end of this article. TRLs have been defined to provide a common metric by which knowledge of new technology’s maturity might be communicated among various engineers, executives, developers and researchers, and among individuals from different organizations. Therefore, TRLs are not linked to a specific technical discipline. The use of TRLs can also provide a needed foundation for developing and communicating insight into the risks involved in advancing a new system, design and its constituent new technology components, and can also be used as a measure of risk associated with introducing new technologies into existing systems This paper considers the need for a higher TRL category, indicating a proven technology demonstrated through extended operational usage, and we have adopted a 1 to 10 scale to make it easier to understand the levels of technological development. The scale can be applied to every project involving technological development.

TRLs for Innovation and development Level 1 – Observe and Report basic principles

This level encompasses ideas and hypotheses where a known fact or process is proposed for a new application. This TRL commences a transition from scientific research to applied research for the development of new technology. Fundamental investigations and paper studies commence.

Level 2 – Applied Research: Formulate technology concept and/or application

At this step in the maturation process, research and development (R&D) is initiated. Practical development actions can then be formulated. Applied research, theory and scientific principles are focused on a specific application area to define the concept and characteristics of the application and specified in a document where functional block diagrams are described clearly. Materials and components are procured at this stage.

Level 3 – Establish critical function, proof of concept

R&D work has begun. Laboratory studies aim to validate analytical predictions of separate components of the technology. This stage is also known as the “breadboarding stage” where demonstration of technical feasibility produces representative data to achieve critical function and/or characteristic proof of concept.

Level 4 – Laboratory testing of prototype component or process

Here, the designs, development and lab testing of various components are integrated to establish that they will work together to achieve the concept-enabling levels of performance required in the final design. They should also be consistent with the requirements of potential system applications. Thus, system-level component and/or breadboard validation in a laboratory environment will identify potential design issues and corrections can be taken at this step.

Level 5 – Alpha testing of the integrated system

The basic technological components (component level, sub-system level or system level) are integrated together with realistic supporting elements to be tested in a simulated or somewhat realistic environment. This prototype stage closely resembles the eventual system and comprises near-finalized electronics or mechanical designs. For example, a new type of solar photovoltaic controller promising higher efficiencies would, at this level, be used in an actual fabricated small-run prototype unit with actually integrated power supplies, protective enclosures, supporting structures, etc., and tested in a simulated environment for data-collection and performance evaluation.

Level 6 – Verify prototype system, begin field testing.

The prototype system is tested and demonstrated in a relevant operational environment where full-scale realistic problems will be observed. If problems arise at this stage, the design must return to TRL 5 or 4 for corrective measures depending on the severity. Engineering feasibility must be fully demonstrated in the actual system application as the design is effectively “locked-in” at this stage and optimized for manufacturability. Ready-to-manufacture (RTM) designs and documentation steps will be carried out to ensure the design is reproducible with the relevant manufacturing steps. Not all technologies will undergo a TRL 6 demonstration. At this point, the maturation step is driven more by assuring management confidence, than by R&D requirements. The demonstration might represent an actual system application, or it might be like the planned application, but using the same technologies.

Level 7 – Demonstrate integrated pilot system, start tooling and manufacturing.

The prototype is near or at the planned operational system level. The final design is virtually complete. The goal of this stage is to remove engineering and manufacturing risks. The system prototype is demonstrated in an operational environment. In this case, the prototype should be near or at the scale of the planned operational system and the demonstration must take place in the actual field environment. This level of maturity indicates system-engineering and development-management confidence. Not all technologies in all systems will go to this level. For example, solar-powered experimental weather nodes for data-gathering are deployed for extended periods of time to gather environmental data but are not slated for mass production or productization.

Level 8 – Incorporate system in commercial design

The technology has been proven to work in its final form under the expected conditions. In most cases, this level represents the end of true system development. The actual system is completed and qualified through tests and demonstration and is submitted for regulatory approvals at this stage. All commercial technologies being applied in actual systems go through TRL 8. In almost all cases, this level is the end of true “system development” for most technology elements. Most user documentation, training documentation and maintenance documentation are completed. All functionality is tested in simulated and operational scenarios. Verification and validation are completed and commercially launched or deployed en masse.

Level 9 – Deploy the system commercially.

The technology in its final form, thoroughly tested and demonstrated, is ready for commercial deployment. The actual system is proven through successful operations in a variety of conditions across a variety of end-users. In almost all cases, this is the end of “bug fixing” and is no longer considered “technology development”. Successful operational experience and sustaining and/or maintenance engineering support mechanisms are put in place.

Level 10 – Commercial Acceptance

The product, process or service has been launched commercially for an extended period, marketed to and adopted by a group of customers (including public authorities). The technology has been used without incident (or with incident levels within an acceptable range) for a protracted period of time. The technology has been certified (if applicable) via appropriate technology-type certification mechanisms, through evaluation of repeated operations and other means. Failure rates for the technology are known and failure conditions and their causes are understood. The technology/system operates without unacceptable levels of unplanned troubleshooting or repair being required.

TRL summary

An illustration of the TRL scale for increasing technology maturity, in the context of the progression from basic research to system operations.

Further Reading on TRL definitions

- NASA TRL definitions

- NASA TRL definitions by John C. Mankins (1995)

- John C. Mankins (2009)

- ESA TRL handbook

- Department of Defense

- US department of energy

- DoD TRA Deskbook

- National Renewable Energy Laboratory– Emerging Technologies in Ocean Kinetic and Enhanced Geo-Thermal

- International Standard (ISO) for TRLs known as ISO16290 here.

- Jeremy Straub TRL 1-10 discussion paper

- European commission “From research to innovation”

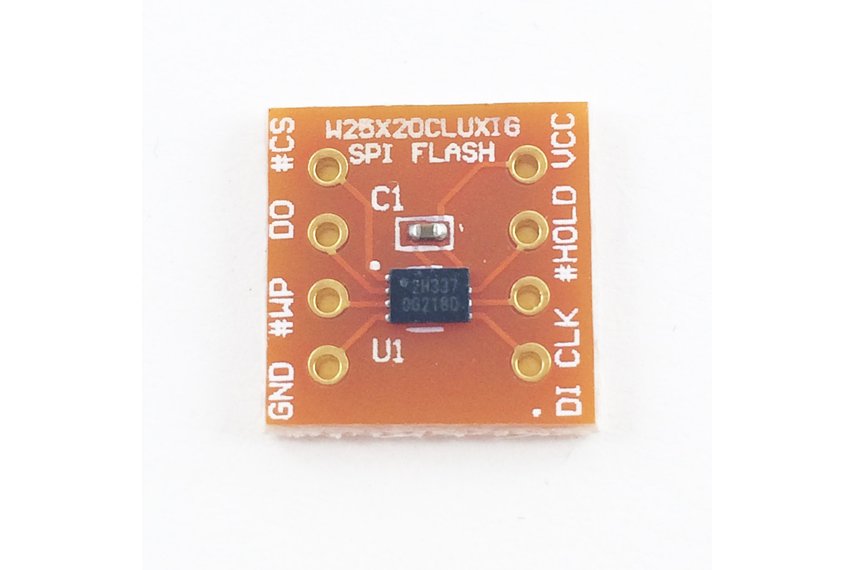

A designer will usually add test pads or programming pads in designs for in-circuit testing with a jig later in the production line.

A designer will usually add test pads or programming pads in designs for in-circuit testing with a jig later in the production line.

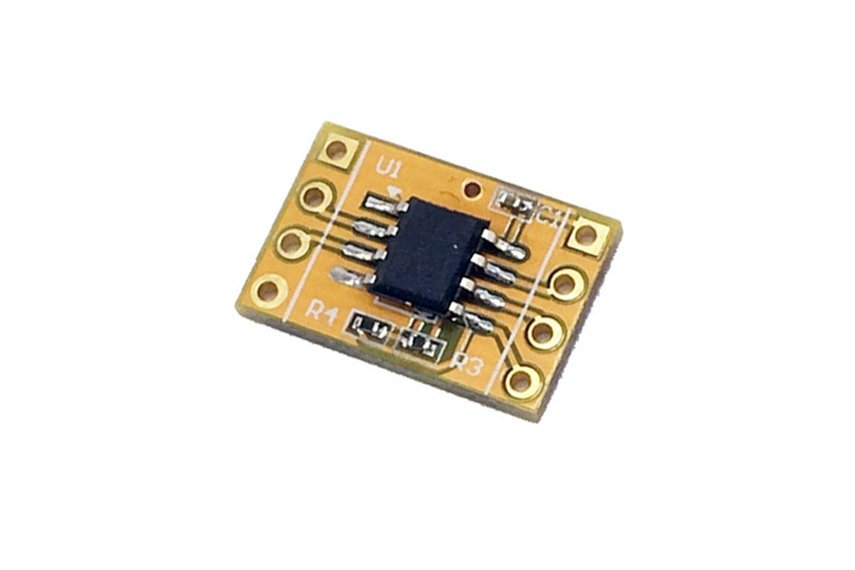

The mechanical structure of the jig is 3D-printed for quick prototyping

The mechanical structure of the jig is 3D-printed for quick prototyping